# **BiSS Interface**

Rev A1, Page 1/2

#### WHY IMPLEMENTING BISS?

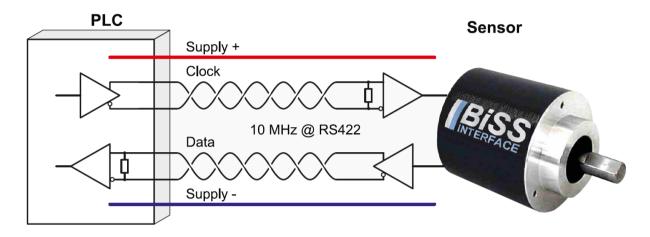

## Structure of a complete BiSS system

Figure 1: BiSS System (point-to-point configuration: master, cable, slave)

## Benefits on using BiSS

- · Open standard

- Non propietory

- Fast

- Serial

- Safe

- Point-to-point capable

- Multi slave bus capable

- Compact

- · Cost effective

- · Permanent bidirectional

- Uses unidirectional lines (e.g. RS422)

- SSI PHY compatible

- SSI backwards compatible/downconfigurable master and slaves

- · Ready-to-use IP modules for device manufacturer

- · Licencing free of charge for device manufacturer

Copyright © 2012 iC-Haus http://www.ichaus.com

## **BiSS Interface**

Rev A1, Page 2/2

#### USING EXISTING EnDAT 2.2™HARDWARE

EnDAT 2.2™does use RS485. Typical EnDAT 2.2™PHY hardware permits bidirectional operation on each line. BiSS does only need unidirectional operation each line as this is a subset of EnDAT 2.2™PHY hardware. BiSS can use existing PHY hardware of an existing EnDAT 2.2™implementation.

#### **USING EXISTING SSI HARDWARE**

SSI does use RS422 unidirectional line drivers. Typical SSI PHY hardware permits unidirectional operation on each line. BiSS does also only need unidirectional operation each line as this is a compatible with SSI PHY hardware. BiSS can use existing PHY hardware of an existing SSI implementation.

#### **USING EXISTING FPGA HARDWARE**

The BiSS master IPs MB101 and MB105 are free available VHDL based BiSS master to be implemented on CPLD/FPGA based hardware.

FPGA Platforms that implemented BiSS master IPs

- XILINX

- ACTEL

- Lattice

- .. other and new platforms that support VHDL or NET LISTS

### USING EXISTING DSP/µC/CPU HARDWARE

The BiSS master IPs MB302 is C/C++ code based BiSS master to be implemented on DSP/µC/CPU hardware.

## DSP/µC/CPU Platforms that implemented BiSS master IPs

- Microchip PIC™

- · Texas Instruments

- SiLabs

- .. other and new platforms that support C/C++ code / structured programming code

#### DSP/µC/CPU Output/Input Interfaces

- GPIO: 2 pins (MA GPIOx output, SL GPIOy input)

- SPI: 2 pins (MA = SCLK, SL = MISO)

- · ... other serial protcol generator hardware

#### **USING EXISTING IC HARDWARE**

- iC-MB3 TSSOP24

- iC-MB4 TSSOP24 (preliminary)

- Custom ASICs

- ... future products with BiSS master functionality